## Memory System Architecture Using Hardware-based Page Replacement

Hanjae Lee, Hyeokjun Seo, and Eui-Young Chung

School of Electrical and Electronic Engineering, Yonsei University, Seoul 120-749, Korea

E-mail: {tmxk37, jjsky7}@dtl.yonsei.ac.kr, eychung@yonsei.ac.kr

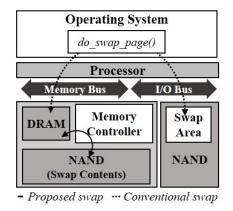

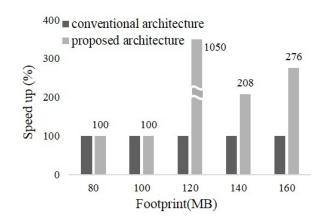

Nowadays, high performance computing is getting more and more important by emerging applications like big-data and cloud computing. Although speed itself accounts for the performance of device is important, architectural support also takes a significant role. Owing to memory capacity limitation, besides, it is not possible to load every necessary data into main memory, causing continuous page swap between memory and storage which are apart from each other. The longer swap path walking through main memory and storage, the bigger waste of processor resource. Accordingly, we focus on improving swap performance of computing system by shortening data path. In this paper, we propose a new memory system architecture exploiting NAND flash memory included in memory system, where page replacement is managed by swap manager connected to DRAM and NAND flash memory. Thereby the processor is no longer required to manage any page fault caused by DRAM capacity. The overall structure is illustrated in Fig 1. We modified gem5 simulator[1] to support the proposed architecture, and set-up 128MB of main memory and plenty of swap area. Fig 2 shows normalized execution times for conventional and the proposed architecture for benchmarks which having different footprints. We observed the proposed architecture is at least twice as fast where DRAM capacity is insufficient.

Fig 1. Structure of proposed system

Fig 2. Simulation result

**Acknowledgement:** This work was supported in part by the IC Design Education Center (IDEC) and by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (2013R1A1A2011208).

[1] Binkert, N., Beckmann, B., Black, G., Reinhardt, S. K., Saidi, A., Basu, A & Wood, D. A. (2011). The gem5 simulator. ACM SIGARCH Computer Architecture News, 39(2), 1-7